## NANO LETTERS 2007 Vol. 7, No. 5 1134–1137

## Toward Self-Assembled Ferroelectric Random Access Memories: Hard-Wired Switching Capacitor Arrays with Almost Tb/in.<sup>2</sup> Densities

Paul R. Evans,<sup>†</sup> XinHau Zhu,<sup>†</sup> Paul Baxter,<sup>†</sup> Mark McMillen,<sup>†</sup> John McPhillips,<sup>†</sup> Finlay D. Morrison,<sup>‡,§</sup> James F. Scott,<sup>‡</sup> Robert J. Pollard,<sup>†</sup> Robert M. Bowman,<sup>†</sup> and J. Marty Gregg\*,<sup>†</sup>

Centre for Nanostructured Media, School of Maths and Physics, Queen's University Belfast, Belfast BT7 1NN, United Kingdom, and Department of Earth Sciences, University of Cambridge, Cambridge CB2 3EQ, United Kingdom

Received November 6, 2006; Revised Manuscript Received March 15, 2007

## **ABSTRACT**

We report on the successful fabrication of arrays of switchable nanocapacitors made by harnessing the self-assembly of materials. The structures are composed of arrays of 20–40 nm diameter Pt nanowires, spaced 50–100 nm apart, electrodeposited through nanoporous alumina onto a thin film lower electrode on a silicon wafer. A thin film ferroelectric (both barium titanate (BTO) and lead zirconium titanate (PZT)) has been deposited on top of the nanowire array, followed by the deposition of thin film upper electrodes. The PZT nanocapacitors exhibit hysteresis loops with substantial remnant polarizations, while although the switching performance was inferior, the low-field characteristics of the BTO nanocapacitors show dielectric behavior comparable to conventional thin film heterostructures. While registration is not sufficient for commercial RAM production, this is nevertheless an embryonic form of the highest density hard-wired FRAM capacitor array reported to date and compares favorably with atomic force microscopy read—write densities.

The importance of data storage to the smooth operation of the modern world has meant that a great deal of research into different memory technologies has been an ongoing high-profile theme in both industry and academic research laboratories. One of the many driving factors influencing this research has been the quest to replace dynamic random access memory (DRAM), and to some extent the combination of DRAM and hard drives, with nonvolatile random access memory (NVRAM). Use of NVRAM as the so-called "universal memory" would both obviate the need to continuously refresh data held in DRAM and avoid the rather awkward interplay between the DRAM chips and ferromagnetic hard drives.

While there are many candidates for future NVRAM, those involving permanent charge storage in capacitor structures, using ferroelectric materials, perhaps represent the most natural progression from DRAM, and indeed, low-density forms of ferroelectric RAM (FRAM) are already in com-

sively more expensive and more difficult to implement as feature sizes of electronic elements decrease into the realms of tens of nanometers. The lithography associated with top-down fabrication can also significantly compromise func-

mercial use.3,4 There is also interest in ferroelectric-based

As with all forms of electronic devices, miniaturization

and reductions in production cost are constant driving forces

in memory development. Unfortunately though, standard

"top-down" photolithographic processing becomes progres-

media as a variation on magnetic hard disk technology.5

of tens of nanometers. The lithography associated with top-down fabrication can also significantly compromise functional properties; damage due to aggressive etching environments, particularly at feature edges and peripheral chip areas, can cause significant variations in, for example, switching behavior of ferroelectric capacitors.<sup>6,7</sup> When coupled with the need for more sensitivity to the amount of switched charge in nanometer feature size FRAMs, edge damage can have dramatic ramifications for reliability. Nanoscale miniaturization therefore comes at a price unless the thermodynamics and kinetics of material behavior can be used to create nanoscale electronic devices without any top-down patterning. Attempting to do exactly this, through "self-assembly", has been an area of intense recent research.<sup>8</sup> Within the field of nanoscale ferroelectric capacitors alone,

<sup>\*</sup> Corresponding author. E-mail: m.gregg@qub.ac.uk.

<sup>†</sup> Queen's University Belfast.

<sup>&</sup>lt;sup>‡</sup> University of Cambridge.

<sup>§</sup> Current address: School of Chemistry, University of St. Andrews, St. Andrews, Fife, KY16 9ST, United Kingdom.

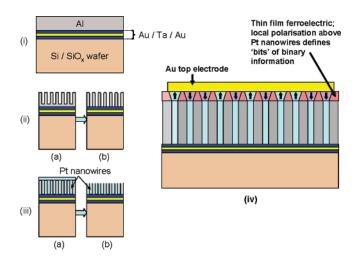

**Figure 1.** Schematic cross-sections of the processing steps associated with the creation of the self-assembled nanocapacitor array: (i) deposition of thin film multilayer electrode and aluminum; (ii) electrolytic anodization of aluminum to form nanopores (a), and NaOH etch (b); (iii) electrolytic deposition of Pt nanowires to the point of overgrowth onto the alumina surface (a), followed by low-angle blanket ion etch (b); (iv) ferroelectric film and top electrode deposition.

several groups have already shown the potential for self-assembly in creating extremely high storage densities.<sup>9–15</sup> However, progress is in its early stages, and working nanoscale "self-assembled" devices are still a long way from becoming a reality.

It is in this context that we report results from a research program in which thin film arrays of nanoscale capacitor structures, hard-wired using Pt nanowires, have been made through self-assembly. The dimensions of the individual capacitor structures, and their lateral spacing, mean that the nominal bit density is of the order of  $10^{11}-10^{12}$  bits per square inch; this sets a new paradigm in hard-wired solid-state memory, and even though similar densities have been demonstrated using scanning probe arrangements,  $^{16-20}$  the advantage of this self-assembled structure is that potentially no moving parts are needed.

A schematic diagram of the processing steps involved in creating the final structure is shown in Figure 1. Initially (Figure 1i), a multilayered tantalum-gold thin film bottom electrode and a thin film (~450 nm) of aluminum were sputter-coated onto a SiO<sub>x</sub>-silicon wafer.<sup>21</sup> The complex multilayered lower electrode was a necessary development to keep reasonable conductivity (through the Au layer) but also have sufficiently strong adhesion between the lower electrode and the substrate so that delamination did not occur during electrolytic anodization of the aluminum. We then placed the coated wafer into a bath of cooled (2 °C) weak sulfuric acid (0.3 M), connecting it up as the anode in an electrolytic circuit using Pt as the cathode. Application of a voltage (20 V) induced the oxidation of the aluminum and the associated formation of nanopores (Figure 1iia).<sup>22</sup> Any alumina at the bottom of the nanopores was removed by a subsequent chemical etch (0.1 M NaOH), locally exposing the lower electrode (Figure 1iib). Then we placed the wafer into another electrolytic cell containing a 0.2 M chloroplatinic

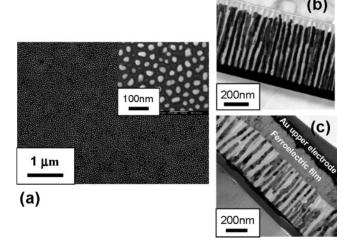

**Figure 2.** Electron microscopy images illustrating the creation of the Pt nanowire arrays (plan-view scanning electron microscopy image (a) and cross-sectional transmission electron microscope (TEM) image (b)); cross-sectional overview (TEM) of the completed nanocapacitor array.

acid salt solution and applied a voltage using a potentiostat. A typical deposition voltage was -0.1 V with respect to a saturated calomel electrode. Because the only conducting regions of electrode exposed to the solution were those at the bottom of the nanopores, electrolytic Pt deposition could only occur within the pores, forming nanowire arrays. The deposition current was monitored during the deposition, and a sudden increase was seen when the wires reached the top of the pores. The deposition was then allowed to continue until the current was no longer increasing, indicating that overgrown wires had merged to form a continuous film on the surface (Figure 1iiia). The sample was then blanket argon ion etched at a low angle to remove this film, leaving the top of the nanowires level with the top of the alumina (Figure 1iiib). Ferroelectric layers were deposited either using pulsed laser deposition (for the barium titanate (BTO); for typical fabrication information, see ref 23) or "misted" chemical solution deposition (for lead zirconium titanate (PZT); for typical fabrication information, see ref 24). Sputtering of gold or platinum upper electrodes completed the structure (Figure 1iv). Figure 2 presents micrographs illustrating the formation of the Pt nanowire array, where clear separation between individual nanowires is evident (plan view image, Figure 2a), as is their relatively straight morphology (cross section image, Figure 2b); Figure 2c shows a cross section of the completed test device. It is noteable that the relatively high processing temperature needed for the oxide ferroelectric layer (~600 °C) causes some degradation to the nanowire morphology. Indeed, in early work where gold nanowires were used, the annealing required for ferroelectric processing caused complete detachment of the nanowires from the Au/Ta/Au lower electrode. Even with Pt nanowires, if ferroelectric processing temperatures are too high (>~650 °C), large areas of detachment occur, as have been noted in cross-sectional TEM and in mapping using surface piezoforce microscopy, where large regions of film could not be poled. Work is ongoing

Nano Lett., Vol. 7, No. 5, **2007**

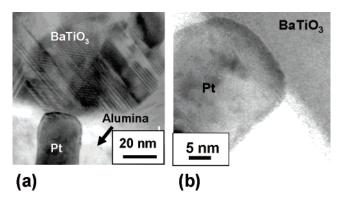

**Figure 3.** Relatively high magnification images (cross-sectional TEM) showing the successful contact between the Pt nanowires and ferroelectric films.

using small amounts of oxygen in the initial aluminum thin film to improve the thermal stability of the pore structures.

The active material for data storage is the ferroelectric thin film, with its state of polarization (either "up" or "down") defining the binary "1" and "0" of the memory. The polarization direction is switched by applying an electric field between the Pt nanowire and the common top electrode. The dimensions of each bit are defined by the field emanating from the tip of each Pt nanowire. The limit for planar bit size is currently driven by the need for the quantity of switched charge to be large enough to be sensed over the parasitic capacitance of the bit-line of the surrounding architecture. For our 20 nm diameter Pt wires, assuming a switchable polarization of  $\sim 50 \,\mu\text{C/cm}^2$  for the ferroelectric, we can estimate the switched charge per bit of only ca. 1.6  $\times$  10<sup>-16</sup> C. This corresponds to  $\sim$ 1000 electrons and is at the present limit for electrical sensing.<sup>25</sup> The nanowires are laterally electrically insulated from each other by alumina and could thus be used as discrete electrodes. In the current structure, the Pt nanowires are not yet individually addressable through the lower electrode, but this is, along with the creation of perfect registry of nanowires, an important area for future development. Our structure does, however, represent a "proof of concept" that nanoscale memory arrays could be constructed without "top-down" patterning.

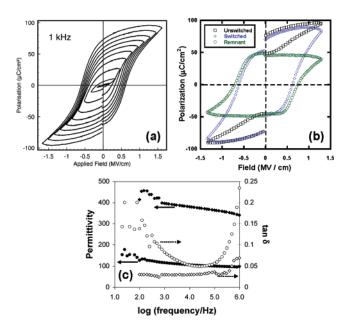

Figure 3 shows transmission electron microscopy (TEM) images of a cross-section of the contact between the Pt nanowires and the ferroelectric layer, critical in making the device operational. Figure 4 illustrates the functional characteristics of the arrays: in the BTO systems, the almost frequency independent behavior of the low-field permittivity, and relatively low dielectric loss, imply that electrically sound capacitor structures have been made. The BTO films were not, however, able to withstand the fields necessary for ferroelectric switching and complete saturation. This contrasts with the PZT-based nanocapacitor arrays, which although being somewhat more lossy, showed genuine switching with remnant polarizations, taken using both Sawyer-Tower (Figure 4a, see ref 26) and the "PUND" measurement techniques (Figure 4b, see ref 27), comparable to bulk (~50  $\mu$ C cm<sup>-2</sup>, see Figure 4b). The slightly high coercive field of ca. 500 kV/cm is not yet understood, but planar features, possibly extremely fine domains, such as those seen clearly

**Figure 4.** Room-temperature polarization-field hysteresis loops (at 1 kHz) from nanocapacitor arrays with PZT as the ferroelectric layer using a Sawyer—Tower circuit (a), $^{26}$  and "PUND" measurement technique (b) $^{27}$  with triangular pulse waveforms. Note the remnant polarization of  $\sim 50~\mu C~cm^{-2}$  obtained through "PUND"; (c) frequency dependence of the low-field relative permittivity and dielectric loss tangent at room temperature for a nanocapacitor array using BaTiO<sub>3</sub> (diamonds) and PbZr<sub>0.4</sub>Ti<sub>0.6</sub>O<sub>3</sub> (circles) as the ferroelectric layer.

in BaTiO<sub>3</sub> (Figure 3a), are frequently observed and may be partly responsible for the disruption of switching.

While the potential for development of this self-assembled nanocapacitor array is exciting, there are several issues needing more work:

- (1) We recognize that the ferroelectric "bits" may require registry and wiring in order to achieve individual addressability. In this work, we sought to investigate and demonstrate the viability of thin film AAO templates, integrated into thin film heterostructures, for creating high-density operational bit storage. Having done this, attention turns to the engineering challenge of registry and electrode addressability. Work is presently underway in this regard using recognized approaches such as imprint lithography on the aluminum film pre-anodization;<sup>28</sup>

- (2) The growth of the ferroelectric needs to be optimized to reduce the coercive fields;

- (3) The thickness of the ferroelectric needs to be significantly reduced so that the polarized regions above each Pt nanowire do not overlap as a result of lateral field-spreading through the ferroelectric film. This needs to be achieved without compromising functional properties.

This third issue has been addressed to some extent. Functional data presented in Figure 4 was for ferroelectric films >100 nm in thickness. Modeling of the potential distribution associated with the nanowire array has been performed using frameworks originally devised for scanning probe microscopy research.<sup>29–31</sup> This shows that, for the films of the order of 100 nm and greater, the system largely behaves as though the nanowires were a continuous lower

1136 Nano Lett., Vol. 7, No. 5, 2007

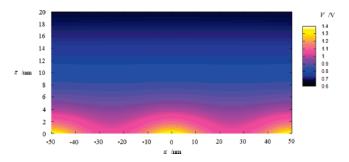

**Figure 5.** Modeled potential distribution above the Pt nanowires in c-axis oriented BaTiO<sub>3</sub> (c-axis perpendicular to the ferroelectric film surface), using approaches used previously for describing potential associated with scanning probe microscopy tips.  $^{29-31}$  Even at  $\sim$ 20 nm, the potential distribution resembles that of a parallel-plate geometry.

electrode, and this conventional geometry was assumed in calculations of both the polarization and permittivity values presented. Furthermore, modeling suggests that, for individual bits to be spatially resolved, the ferroelectric thickness should be considerably thinner, indicated by the potential distribution map shown in Figure 5 for a 20 nm ferroelectric film. Work is currently underway to make films in this ultrathin regime.

In summary, a novel structure has been made in which ferroelectric films have been deposited onto arrays of self-assembled platinum nanowires, laterally electrically isolated from each other by aluminum oxide. The nanowire—ferroelectric interface has been shown to be of sufficient quality that ferroelectric switching can be induced by dropping potential between the nanowire and a common macroscopic upper electrode. The scale of the nanowire array is such that bit densities approach the Tb in.<sup>-2</sup>.

**Acknowledgment.** We acknowledge the Engineering and Physical Sciences Research Council, the Royal Society, and Invest Northern Ireland for financial support of the work.

## References

- (1) Scott, J. F. Ferroelectric Memories; Springer-Verlag: Berlin, 2000.

- (2) Schlatka, B. Nanotechnology Law and Business 2005, 2, 230.

- (3) Scott, J. F.; Morrison, F. D.; Miyake, M.; Zubko, P.; Lou, X.; Kugler, V. M.; Rios, S.; Zhang, M.; Tatsuta, T.; Tsuji O.; Leedham, T. J. J. Am. Ceram. Soc. 2005, 88, 1691.

- (4) Dawber, M.; Rabe, K.; Scott, J. F. Rev. Mod. Phys. 2005, 77, 1083.

- (5) Park, H.; Jung, J.; Min, D.-K.; Kim, S.; Hong, S.; Shin, H. Appl. Phys. Lett. 2004, 84, 1734.

- (6) Jung, D. J.; Morrison, F. D.; Dawber, M.; Kim, H. H.; Kim, K.; Scott, J. F. J. Appl. Phys. 2004, 95, 4968–75.

- (7) Stanishevsky, A.; Aggarwal, A.; Prakash, A. S.; Melngailis, J.; Ramesh, R. J. Vac. Sci. Technol., B 1998, 16, 3899.

- (8) Whitesides, G. M.; Grzybowski, B. Science 2002, 295, 2418.

- (9) Alexe, M.; Scott, J. F.; Curran, C.; Zakharov, N. D.; Hesse, D.; Pignolet, A. Appl. Phys. Lett. 1998, 73, 1592.

- (10) Alexe, M.; Gruverman, A.; Harnagea, C.; Zakharov, N. D.; Pignolet, A.; Hesse, D.; Scott, J. F. Appl. Phys. Lett. 1999, 75, 1158.

- (11) Dawber, M.; Szafraniak, I.; Alexe, M.; Scott, J. F. J. Phys.: Condens. Matter 2003, 15, L667.

- (12) Szafraniak, I.; Harnagea, C.; Scholz, R.; Bhattacharyya, S.; Hesse, D.; Alexe, M. Appl. Phys. Lett. 2003, 83, 2211.

- (13) Ma, W.; Harnagea, C.; Hesse, D.; Gosele, U. Appl. Phys. Lett. 2003, 83, 3770.

- (14) Ma, W.; Hesse, D. Appl. Phys. Lett. 2004, 85, 3214.

- (15) Buhlmann, S.; Muralt, P.; Von, Allmen, S. Appl. Phys. Lett. 2004, 84, 2614.

- (16) Paruch, P.; Tybell, T.; Triscone, J.-M. Appl. Phys. Lett. 2001, 79, 530

- (17) Tybell, T.; Paruch, P.; Giamarchi, T.; Triscone, J.-M. Phys. Rev. Lett. 2002, 89, 097601.

- (18) Tybell, T.; Ahn, C. H.; Triscone, J.-M. Appl. Phys. Lett. 1998, 72, 1454.

- (19) Ahn, W. S.; Jung, W. W.; Choi, S. K.; Cho, Y. Appl. Phys. Lett. 2006, 88, 082902.

- (20) Gruverman, A.; Kholkin, A. Rep. Prog. Phys. 2006, 69, 2443 and references therein.

- (21) Atkinson, R.; Hendren, W. R.; Wurtz, G. A.; Dickson, W.; Zayats, A. V.; Evans, P.; Pollard, R. J. *Phys. Rev. B* 2006, 73, 235402. Evans, P.; Hendren, W. R.; Atkinson. R.; Wurtz, G. A.; Dickson, W.; Zayats, A. V.; Pollard, R. J. *Nanotechnology* 2006, 17, 5746.

- (22) Keller, F.; Hunter, M.; Robinson, D. L.; J. Electrochem. Soc. 1953, 100, 411

- (23) Lookman, A.; McAneney, J.; Bowman, R. M.; Gregg, J. M.; Kut, J.; Rios, S.; Ruediger, A.; Dawber, M.; Scott, J. F. Appl. Phys. Lett. 2004, 85, 5010. Sinnamon, L. J.; Bowman, R. M.; Gregg, J. M. Appl. Phys. Lett. 2001, 78, 1724.

- (24) McMillan, L. D.; Paz, de Araujo, C. A.; Roberts, T.; Cuchiaro, J.; Scott, M. C.; Scott, J. F. *Integr. Ferroelectr.* 1992, 2, 351.

- (25) Alexe, M. private communication

- (26) The Sawyer—Tower methodology for measurement of ferroelectric hysteresis, in its simplest form (Sawyer, C. B.; Tower, C. H. *Phys. Rev.* **1930**, *35*, 269), uses a reference capacitor in series with the capacitor under test (CUT). Measurement of the voltage across the reference capacitor allows calculation of the charge, given that this reference capacitance is known, and because the capacitors are in series, this is also the charge developed on the CUT. From the value of charge, and geometric considerations of the sample, polarization can be calculated, and because the voltage across the CUT can be measured directly, the electric field can also be determined, hence *P*–*E* loops for the CUT can be measured. Modifications to the basic Sawyer—Tower circuit have also been successfully developed (e.g., Diamant, H., Drenck, K., Pepinsky, R. *Rev. Sci. Instrum.* **1957**, 28, 30).

- (27) The "PUND" measurement technique (Scott, J. F.; Kammerdiner, L.; Parris, M.; Traynor, S.; Ottenbacher, V.; Shawabkeh, A.; Oliver, W. F. J. Appl. Phys. 1988, 64, 787) involves sending a series of five voltage pulses across the capacitor under test and monitoring the electrical current generated. The first pulse is used to pole the ferroelectric in a particular sense (taken as "negative" or "downwards") and current is not monitored; the next pulse is in the opposite sense (positive "P") and should switch the direction of polarization in the ferroelectric. The switching current and all other nonswitching currents associated with leakage, development of nonswitching polarization, etc., are included in this signal; the next pulse is also in the positive (or upwards "U") sense but does not cause switching, as the ferroelectric is already poled in the positive direction and therefore allows all the nonswitching current to be measured directly. This sequence is then repeated in the negative sense: "N" for the negative switching pulse, and "D" (for downwards) for the negative nonswitching pulse. Subtraction of the integrated current for "P" and "U" pulses gives the switching charge in the positive direction and between "N" and "D" gives switching charge in the negative direction, and hence the polarization developed as a result of switching only can be determined.

- (28) Choi, J.; Nielsch, K.; Reiche, M.; Wehrspohn, R. B.; Gösele, U. J. Vac. Sci. Technol., B 2003, 21, 763.

- (29) Mele, E. J. Am. J. Phys. 2001, 69, 557.

- (30) Molotskii, M. J. Appl. Phys. 2003, 93, 6234.

- (31) Kalinin, S. V.; Karapetian, E.; Kachanov, M. Phys. Rev. B 2004, 70, 184101.

NL0626028

Nano Lett., Vol. 7, No. 5, **2007**